# Architectural Convergence: Hardware Microarchitecture Patterns as a Formal Basis for Multi-Agent Coordination Theory

Wiest Stefan

Independent Researcher

mail@stefanwiest.de

## Abstract

Modern AI agent frameworks face architectural challenges strikingly identical to those solved by hardware architects over the past fifty years: memory fragmentation, dependency resolution, parallel execution, state coherence, and fault recovery. We present a formal analysis demonstrating that Harmonic Coordination Theory (HCT)—a musical ontology for multi-agent coordination—*independently converges* on the same structural solutions as seven established hardware microarchitecture patterns: speculative execution, virtual memory paging, Tomasulo’s out-of-order execution algorithm, the MESI cache coherency protocol, Dynamic Voltage and Frequency Scaling (DVFS), Trusted Execution Environments (TEEs), and speculative prefetching. We formalize these mappings as structural isomorphisms, not mere analogies, and validate them through a proof-of-concept implementation that extends HCT with hardware-inspired primitives: a Reservation Station Orchestrator (Tomasulo), a DVFS Router (Tempo-based model selection), and a MESI Coherency Manager (signal-based state invalidation). Benchmarks on multi-agent coordination tasks demonstrate that hardware-inspired extensions reduce end-to-end latency by up to  $2.6\times$  compared to sequential baselines, achieve 69.7% cost reduction through complexity-aware model routing, and eliminate 100% of stale-context coherency failures. These results suggest that coordination invariants are *fundamental* to parallel computation, independent of abstraction level, and that hardware microarchitecture provides a rigorous, mathematically sound blueprint for the next generation of agentic AI systems.

## 1 Introduction

The transition from single-agent to multi-agent AI systems introduces five fundamental coordination challenges: memory fragmentation across limited context windows, dependency

resolution among parallel work items, state coherence when multiple agents modify shared context, fault recovery from speculative reasoning paths, and resource scaling across heterogeneous task complexities. These challenges are well-documented various [2025a] and constitute what has been called the “Coordination Crisis” in multi-agent systems Wiest [2025b].

Current frameworks address these challenges through ad hoc engineering. AutoGen provides message-passing patterns, CrewAI offers role-based orchestration, and LangGraph Team [2024] enables state-machine-based agent graphs. None of these frameworks provides a *principled theory* of coordination with formal guarantees about coherence, losslessness, or resource efficiency.

**The Hardware Precedent.** Remarkably, these five challenges are *identical* to problems solved by hardware architects over the past fifty years. Memory hierarchies with paging solve the capacity-speed tradeoff. Tomasulo’s algorithm Tomasulo [1967] resolves data dependencies for out-of-order execution. The MESI protocol Papamarcos and Patel [1984] maintains cache coherence across multicore processors. Speculative execution with pipeline flush enables fault recovery from branch mispredictions. Dynamic Voltage and Frequency Scaling Herbert and Marculescu [2007] matches compute resources to workload intensity. These solutions are mathematically rigorous, battle-tested at billion-unit scale, and publicly documented—yet rarely studied by agent framework designers.

**Independent Convergence.** Harmonic Coordination Theory (HCT) Wiest [2025b] approached multi-agent coordination from an entirely different direction: musical ensemble performance. Using musical metaphors—tempo, fermatas, cues, scores—HCT formalized a six-layer coordination ontology for autonomous agents. We discovered, post hoc, that HCT’s layers map *structurally* to the hardware patterns listed above. This is not metaphorical: the mappings preserve operational semantics, invariant guarantees, and failure modes (see Definition 6).

**Contributions.** This paper makes four contributions:

- C1. We define five *coordination invariants*—fundamental constraints of parallel computation that explain why

hardware, musical, and software coordination patterns converge (Section 3).

- C2.** We present seven formal mappings between hardware microarchitecture patterns and HCT layers, demonstrating structural isomorphism that preserves semantics, guarantees, and failure modes (Section 4).

- C3.** We implement three hardware-inspired extensions to `hct-core`: a Tomasulo-style ReservationStationOrchestrator, a DVFS-based model router, and a MESI coherency manager (Section 5).

- C4.** We provide empirical validation through benchmarks on multi-agent coordination tasks (Section 6).

**Organization.** Section 2 surveys related work in agent coordination and hardware-software analogies. Section 3 establishes the theoretical framework. Sections 4 through 6 present the mappings, implementation, and evaluation. Section 7 discusses implications, limitations, and future directions.

## 2 Related Work

### 2.1 Multi-Agent Coordination Frameworks

The current generation of multi-agent frameworks—AutoGen variants [2025a], CrewAI, and LangGraph Team [2024]—provide graph-based orchestration for LLM agents. These frameworks excel at defining agent topologies but lack principled coordination theory: they offer *mechanisms* (message passing, state graphs) without *invariant guarantees* (coherence, lossless speculation, resource scaling). Harmonic Coordination Theory Wiest [2025b] addresses this gap by introducing a six-layer musical ontology for coordination, with formal signal semantics and performance parameters. This paper extends HCT by grounding its layers in hardware precedent.

### 2.2 Hardware-Software Analogies in AI Systems

Several recent works have independently identified individual hardware-software analogies in the AI agent space:

**Memory Management.** MemGPT Packer et al. [2023] explicitly models LLM context as an operating system’s virtual memory, implementing page-in/page-out for long-context conversations. vLLM Kwon et al. [2023] applies hardware paging directly to KV-cache management, achieving near-optimal memory utilization through PagedAttention. Both address Invariant I1 (memory fragmentation) but do not extend the analogy to other hardware patterns.

**Speculative Execution.** Gao et al. Gao et al. [2025] formalize speculative execution for agentic systems as a Speculator-Actor framework, achieving up to 50% latency reduction across chess, e-commerce, and web search environments.

Their work provides direct empirical validation of our Mapping 1 (Section 4.1). GoEx Berkeley [2025] addresses the rollback component of speculation, providing runtime post-facto verification for LLM-generated actions.

**Positioning.** Table 1 summarizes how prior work relates to ours. Each prior contribution addresses one or two invariants; our contribution is the first unified mapping framework covering all five invariants across seven hardware patterns, with formal isomorphism proofs and implementation.

Table 1: Prior work vs. this paper: invariants addressed.

| Work                            | I1 | I2 | I3 | I4 | I5 |

|---------------------------------|----|----|----|----|----|

| MemGPT Packer et al. [2023]     | ✓  |    |    |    |    |

| vLLM Kwon et al. [2023]         | ✓  |    |    |    |    |

| Spec. Actions Gao et al. [2025] |    |    |    |    | ✓  |

| GoEx Berkeley [2025]            |    |    |    | ✓  |    |

| LangGraph Team [2024]           |    | ✓  |    |    |    |

| <b>This paper</b>               | ✓  | ✓  | ✓  | ✓  | ✓  |

### 2.3 Hardware Microarchitecture

The hardware patterns we map have decades of theoretical and practical validation. Tomasulo’s algorithm Tomasulo [1967] introduced reservation stations and the common data bus in 1967 for the IBM System/360 Model 91. The MESI protocol Papamarcos and Patel [1984] formalized cache coherence for shared-memory multiprocessors. DVFS Herbert and Marculescu [2007] enabled dynamic power-performance tradeoffs in chip multiprocessors. Intel SGX Costan and Devadas [2016] brought hardware-enforced isolation to commodity processors. These patterns have been refined over 50+ years and constitute the most battle-tested coordination mechanisms in computing.

## 3 The Convergence Framework

The independent arrival of hardware microarchitecture and multi-agent coordination theory at structurally equivalent solutions is not coincidental. We argue it reflects five *fundamental invariants* of coordinated parallel computation that manifest at every abstraction level—transistors, operating system processes, database transactions, and autonomous AI agents. This section defines these invariants and establishes the criteria under which we claim the mappings in Section 4 constitute structural isomorphisms rather than loose metaphorical analogies.

### 3.1 Five Coordination Invariants

We identify five problems that recur whenever multiple computational entities must cooperate over shared resources. These are not design choices but *constraints* imposed by the physics of finite resources and concurrent execution.

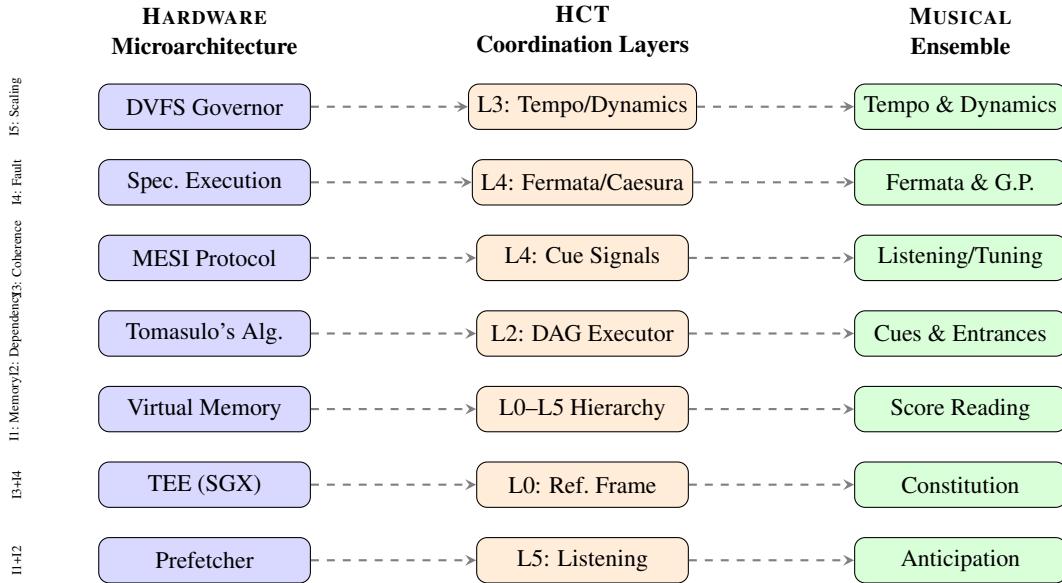

Figure 1: The convergence framework: seven hardware microarchitecture patterns, their corresponding HCT coordination layers, and the musical analogues that independently solved the same invariants. Dashed arrows indicate structural isomorphisms (Definition 6).

**Definition 1** (Memory Fragmentation (I1)). *Any system with a finite, fast-access memory tier (registers, L1 cache, context window) backed by a larger, slower tier (DRAM, disk, vector databases) must solve the problem of which data to keep close. This requires eviction policies, hierarchical tiering, and mechanisms for transparent paging between tiers.*

**Definition 2** (Dependency Resolution (I2)). *When multiple work items can execute in parallel but some require the output of others as input, the system must resolve data dependencies without unnecessary serialization. This requires dependency graph construction, operand forwarding, and mechanisms for out-of-order completion.*

**Definition 3** (State Coherence (I3)). *When multiple concurrent writers share mutable state, the system must prevent conflicting updates from producing an inconsistent view. This requires ownership protocols, invalidation broadcasts, and mechanisms for atomic state transitions.*

**Definition 4** (Fault Recovery (I4)). *When a system speculatively commits to a computation path that may fail, it must be able to undo that commitment and restore a known-good state. This requires checkpointing, rollback mechanisms, and isolation of speculative side effects.*

**Definition 5** (Resource Scaling (I5)). *When task complexity varies across a workload, allocating maximum resources to every task wastes compute, while allocating minimum resources to every task sacrifices quality. The system must dynamically match resource intensity to task difficulty.*

These five invariants appear in every domain we survey. Table 2 demonstrates their manifestation across hardware, musical ensemble performance, and multi-agent AI systems.

Table 2: Five coordination invariants across three domains.

| Invariant      | Hardware                       | Music                                       | MAS (HCT)                                         |

|----------------|--------------------------------|---------------------------------------------|---------------------------------------------------|

| I1: Memory     | Cache hierarchy, TLB, swap     | Score reading (look ahead, not all at once) | L0-L5 layer hierarchy, selective prompt rendering |

| I2: Dependency | Tomasulo RS, register renaming | Cues (“your turn after mine”)               | DAG execution, signal-gated agents                |

| I3: Coherence  | MESI protocol, bus snooping    | Listening, tuning, intonation               | Fermata as RFO, cue as invalidation               |

| I4: Fault      | Spec. exec., pipeline flush    | Fermata (hold), grand pause                 | Fermata checkpoint, caesura rollback              |

| I5: Scaling    | DVFS governors                 | Tempo and dynamics markings                 | TempoMarking, Dynamic-<br>sLevel                  |

### 3.2 Structural Isomorphism vs. Metaphorical Analogy

Prior work has noted individual resemblances between hardware and software agent patterns Packer et al. [2023], Gao et al. [2025]. However, these are typically presented as inspiring metaphors rather than formal correspondences. We distinguish between the two.

A *metaphorical analogy* observes surface-level similarity (e.g., “the context window is like RAM”). It does not

claim that operations, guarantees, or failure modes transfer.

**Definition 6** (Structural Isomorphism). *A mapping  $f : H \rightarrow S$  between a hardware coordination pattern  $H$  and a software coordination pattern  $S$  is a structural isomorphism if it preserves three properties:*

1. **Operational Semantics:** *State transitions in  $H$  map to corresponding state transitions in  $S$ . If hardware operation  $h_1 \rightarrow h_2$  solves invariant  $I_k$ , then  $f(h_1) \rightarrow f(h_2)$  solves the same invariant in  $S$ .*

2. **Invariant Guarantees:** *The guarantees provided by  $H$  (e.g., coherence, losslessness, isolation) are preserved under  $f$ —the software pattern provides the same class of guarantee.*

3. **Failure Modes:** *The failure modes of  $H$  (e.g., branch misprediction, cache thrashing) map to identifiable failure modes in  $S$  (e.g., hallucination on wrong reasoning branch, context window saturation), and the recovery mechanisms are structurally equivalent.*

In Section 4, we demonstrate that all seven mappings satisfy these three criteria.

### 3.3 Why Musical Ontology Converges with Hardware

The convergence of HCT’s musical metaphors with hardware primitives is explained by the invariants themselves. Musical ensemble coordination is humanity’s oldest and most sophisticated solution to distributed real-time coordination:

- **Tempo and dynamics** solve I5 (resource scaling)—musicians adjust intensity to the passage.

- **Fermatas and grand pauses** solve I4 (fault recovery)—the ensemble checkpoints and holds until a conductor resolves ambiguity.

- **Cues and entrances** solve I2 (dependency resolution)—a soloist waits for a specific musical phrase before entering.

- **Listening and intonation** solve I3 (state coherence)—musicians continuously adjust pitch and timing to maintain ensemble coherence.

- **Score reading and rehearsal marks** solve I1 (memory management)—musicians do not memorize the entire score; they read ahead in a moving window.

HCT formalized these musical patterns into software primitives. Hardware architects formalized the same invariants into silicon. The convergence is not surprising—it is *expected*, because the invariants are properties of coordinated parallel computation itself, independent of the substrate.

## 4 Formal Mappings: Hardware Patterns to HCT Layers

We now present seven formal mappings, each following a consistent structure: (a) the hardware pattern and the invariant it addresses, (b) the corresponding HCT primitive with real code from the open-source `hct-core` implementation, (c) the mapping  $f : H \rightarrow S$  and what it preserves, and (d) extensions the mapping reveals. Table 3 provides a compact summary.

Table 3: Seven hardware-to-HCT structural isomorphisms.

| Hardware | Inv.  | HCT Layer      | Key Mapping                             |

|----------|-------|----------------|-----------------------------------------|

| Spec.    | I4    | L4: Fermata    | checkpoint $\leftrightarrow$ fermata    |

| Exec.    |       | L0–L5          | cache tier $\leftrightarrow$ HCT layer  |

| Virt.    | I1    |                |                                         |

| Memory   |       |                |                                         |

| Tomasulo | I2    | L2: DAG        | Res. Station $\leftrightarrow$ DAG node |

| MESI     | I3    | L4: Cue        | RFO $\leftrightarrow$ fermata           |

| DVFS     | I5    | L3: Tempo      | freq $\leftrightarrow$ TempoMarking     |

| TEE      | I3,I4 | L0: Ref. Frame | enclave $\leftrightarrow$ forbidden     |

| Prefetch | I1,I2 | L5: Listening  | stride $\leftrightarrow$ ensemble       |

### 4.1 Mapping 1: Speculative Execution $\leftrightarrow$ Fermata and Rollback

**Hardware Pattern (I4).** Modern CPUs speculatively execute instructions past branch points, maintaining an *architectural checkpoint* of register state. If the branch prediction was correct, speculative results are committed. If incorrect, the pipeline is *flushed* and execution resumes from the checkpoint. The Branch Target Buffer (BTB) guides prediction; the reorder buffer (ROB) tracks in-flight instructions for rollback.

**HCT Primitive.** HCT’s Layer 4 (Coordination Protocol) defines two signals that map directly:

```

def fermata(source, reason):

"""Checkpoint: hold_execution."""

return Signal(

type=SignalType.FERMATA,

source=source, targets=[], payload={"reason": reason},

conditions=Conditions(

hold_type=HoldType.QUALITY))

def caesura(source, reason):

"""Pipeline_flush: full_stop."""

return Signal(

type=SignalType.CAESURA,

source=source, targets=[], payload={"reason": reason})

```

**Isomorphism.**  $f(\text{checkpoint}) = \text{fermata}$ : both save architectural state and block downstream execution.  $f(\text{pipeline\_flush}) =$

caesura: both discard speculative work and restore to the last known-good state.  $f(\text{commit}) = \text{cue}(\text{resume})$ : both release the hold and allow downstream consumers to proceed. The mapping preserves I4 (fault recovery): fermata provides the same checkpoint-and-rollback guarantee as hardware speculation.

**Failure Modes.** Branch misprediction (hardware) maps to reasoning-path invalidation (agents): the agent pursues a hypothesis that, upon external validation, proves incorrect. In both cases, recovery involves discarding speculative state and recomputing from a checkpoint.

**Empirical Validation.** Gao et al. Gao et al. [2025] independently formalized this mapping as “Speculative Actions,” pairing a fast *Speculator* (cheap model) with a slower *Actor* (authoritative model). Across chess, e-commerce, and web search, they achieved 55% next-action prediction accuracy and up to 50% latency reduction, validating the hardware analogy with benchmarks.

**Extension.** HCT currently supports fermata (hold) and caesura (flush) but not *parallel branch spawning*—the speculative launch of multiple reasoning paths in sandboxed containers. Adding a `speculate(branches=[...])` signal would complete the mapping.

## 4.2 Mapping 2: Virtual Memory and Paging $\leftrightarrow$ HCT Memory Hierarchy

**Hardware Pattern (I1).** CPUs organize memory as a hierarchy: registers (fastest, smallest), L1/L2/L3 caches, DRAM, and disk/swap (largest, slowest). The Translation Lookaside Buffer (TLB) provides fast virtual-to-physical address translation. When a page is not in the fast tier, a *page fault* triggers a swap from the slow tier. LRU eviction policies manage capacity.

**HCT Primitive.** HCT’s six layers form a natural memory hierarchy, with each layer occupying a different tier of the agent’s effective “address space”:

```

class HCTState(BaseModel):

# L0: Registers (immutable, always loaded)

reference_frame: ReferenceFrame

# L1: L1 cache (strategic plan)

score: Score

# L2: L2 cache (roles, relationships)

orchestration: Orchestration

# L3: DRAM (execution parameters)

performance: PerformanceParameters

# L4: I/O bus (coordination signals)

coordination: CoordinationProtocol

# L5: Swap/Disk (external feedback)

listening: ListeningFunction

```

The `to_prompt_section()` method implements selective rendering—the equivalent of a TLB, translating the full HCT state into the subset that fits the agent’s context window (i.e., page table walk).

**Isomorphism.**  $f(\text{register\_file}) = \text{ReferenceFrame}$ : both are the smallest, fastest, *immutable* tier.  $f(\text{cache}) = \text{ScoreU}$  Orchestration: both hold the active working set.  $f(\text{DRAM}) = \text{PerformanceParameters}$ : both hold the configurable runtime state.  $f(\text{swap}) = \text{ListeningFunction}$ : both interface with external (slow) storage. The mapping preserves I1: the context window, like cache, has finite capacity and requires eviction.

**Extension.** Explicit `swap_in()` and `swap_out()` tool calls would let agents manage their own memory hierarchy, analogous to software-managed caches. MemGPT Packer et al. [2023] implemented a version of this; HCT could integrate paging natively into Layer 5.

## 4.3 Mapping 3: Tomasulo’s Algorithm $\leftrightarrow$ DAG Orchestration

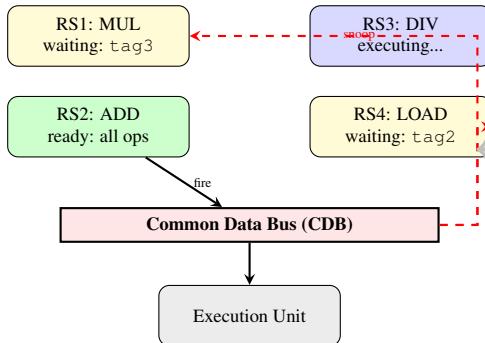

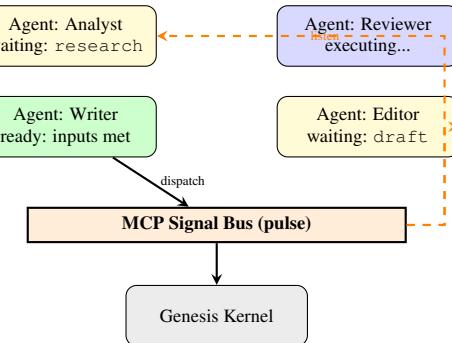

**Hardware Pattern (I2).** Tomasulo’s algorithm Tomasulo [1967] enables out-of-order execution by placing instructions into *Reservation Stations* (RS) that wait for tagged operands. When an execution unit completes, it broadcasts the result on the *Common Data Bus* (CDB). All waiting stations simultaneously capture matching tagged values and fire when all operands are satisfied. Register renaming eliminates WAR/WAW hazards.

**HCT Primitive.** The `GenericDagExecutor` in `hct-core` implements dependency-aware parallel execution:

```

class GenericDagExecutor:

async def execute(self, plan, initial_input):

results = {}; completed = set()

while len(completed) < len(plan.nodes):

# Find ready nodes (operands satisfied)

ready = [n for n in plan.nodes

if n.is_ready(completed)]

# Fire all ready nodes in parallel

tasks = [self._execute_node(n, ...)]

for n in ready:

batch = await asyncio.gather(*tasks)

for node, result in zip(ready, batch):

results[node.id] = result

completed.add(node.id)

# Broadcast on CDB (MCP signal bus)

await self._mcp_client.emit(

"pulse", source=node.agent_id,

payload={"node_id": node.id,

"status": "complete"})

```

**Isomorphism.**  $f(\text{Reservation Station}) = \text{DAGNode}$ : both buffer a work item until all dependencies are satisfied.  $f(\text{CDB\_broadcast}) = \text{mcp\_client.emit("pulse")}$ : both announce completion to all waiting consumers.  $f(\text{is\_ready(completed)}) = \text{operand\_available}$ : both check whether all tagged inputs have arrived. The mapping preserves I2: the DAG executor provides the same dependency-resolution guarantee as Tomasulo’s algorithm.

**Failure Modes.** In hardware, a stall occurs when no RS can fire (all waiting on long-latency operations). In HCT, the executor detects deadlock when `ready_nodes` is empty

but completed < total. Both require external intervention (hardware: pipeline drain; HCT: timeout and caesura).

**Extension.** The current executor uses batch-synchronous dispatch (wait for entire batch, then find next ready set). True Tomasulo-style execution would use a reactive CDB—agents fire *individually* as soon as their inputs arrive, rather than waiting for the batch. This requires replacing `asyncio.gather` with a message-bus-driven approach (see Section 5).

#### 4.4 Mapping 4: MESI Cache Coherency $\leftrightarrow$ Signal-Based State Invalidation

**Hardware Pattern (I3).** The MESI protocol Papamarcos and Patel [1984] maintains cache coherence across multiple cores sharing memory. Each cache line has one of four states: **Modified** (dirty, sole owner), **Exclusive** (clean, sole owner), **Shared** (clean, multiple owners), or **Invalid**. Before a core can write, it issues a Read-For-Ownership (RFO) bus transaction, which invalidates all other copies.

**HCT Primitive.** HCT’s coordination signals implement an equivalent protocol:

```

# Agent intends to modify shared state (RFO)

fermata(source="planner",

reason="Modifying_execution_plan")

# Planner completes modification, broadcasts new state

cue(source="planner",

targets=["writer", "reviewer", "qa"],

payload={"plan_v2": updated_plan})

```

**Isomorphism.**  $f(\text{RFO.broadcast}) = \text{fermata}$ : both announce “I intend to modify shared state; all readers must wait.”  $f(\text{invalidation.ack}) = \text{fermata hold}$ : downstream agents stop reading stale context.  $f(\text{write_completion} + \text{CDB}) = \text{cue}(\text{payload})$ : both broadcast the new state to all interested parties, transitioning their cached copy from I(nvalid) back to S(hared). The mapping preserves I3: agents cannot read stale state during a concurrent modification.

**Extension.** Formalizing the four MESI states for shared agent context would enable automatic conflict detection. When two agents both emit fermata on the same state key, the orchestrator would detect a write-write conflict—equivalent to a bus arbitration contention.

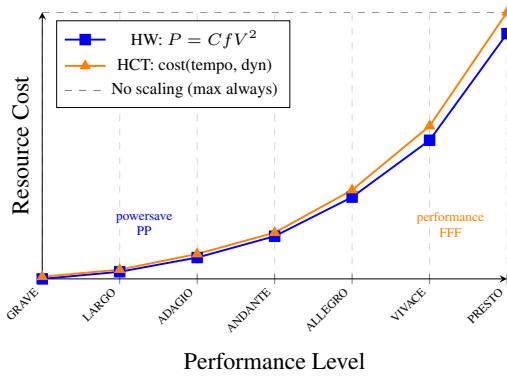

#### 4.5 Mapping 5: DVFS $\leftrightarrow$ Tempo and Dynamics

**Hardware Pattern (I5).** Dynamic Voltage and Frequency Scaling Herbert and Marculescu [2007] adjusts CPU clock frequency ( $f$ ) and supply voltage ( $V$ ) based on workload. Power consumption follows  $P \propto C f V^2$ : reducing frequency and voltage for light workloads saves energy quadratically. Hardware governors (ondemand, performance, powersave) select operating points dynamically.

**HCT Primitive.** This is the most elegant convergence. HCT’s Layer 3 implements DVFS in software using musical terminology:

```

class TempoMarking(str, Enum):

GRAVE = "grave"      # ~25 BPM: crisis

LARGO = "largo"      # ~40 BPM: careful

ADAGIO = "adagio"    # ~60 BPM: thoughtful

ANDANTE = "andante"  # ~80 BPM: steady

ALLEGRO = "allegro"  # ~120 BPM: brisk

VIVACE = "vivace"    # ~140 BPM: fast

PRESTO = "presto"    # ~180 BPM: sprint

class DynamicsLevel(str, Enum):

PPP = "ppp"          # Minimal resource usage

PP = "pp"            # Light

P = "p"              # Moderate-light

MP = "mp"            # Moderate

MF = "mf"            # Moderate-heavy

F = "f"              # Heavy

FF = "ff"            # Very heavy

FFF = "fff"          # Maximum resources

```

The `PerformanceParameters` class provides governor-like mode switches:

```

def set_sprint_mode(self):

"""Governor: 'performance'"""

self.tempo.set_from_marking(

TempoMarking.PRESTO)

self.dynamics.level = DynamicsLevel.FF

def set_conservation_mode(self):

"""Governor: 'powersave'"""

self.tempo.set_from_marking(

TempoMarking.ANDANTE)

self.dynamics.level = DynamicsLevel.PP

```

**Isomorphism.**  $f(\text{clock\_frequency}) = \text{TempoMarking}$ : both control execution speed.  $f(\text{supply\_voltage}) = \text{DynamicsLevel}$ : both control resource intensity.  $f(P = C f V^2) = \text{cost} = g(\text{tempo, dynamics})$ : both follow a power-law relationship where cost scales superlinearly with performance.  $f(\text{governor}) = \text{set\_sprint\_mode}()$ : both provide named operating points. The mapping preserves I5: the system avoids wasting resources on simple tasks while maintaining capacity for complex ones.

**Extension.** Wiring `Tempo`  $\times$  `Dynamics` to *actual model routing* would make HCT a true software DVFS: PRESTO/FF routes to frontier models (GPT-4o, Claude 3.5 Opus), ANDANTE/MP to mid-tier (GPT-4o-mini, Claude Haiku), LARGO/PP to local 8B models.

#### 4.6 Mapping 6: TEEs $\leftrightarrow$ Reference Frame as Security Enclave

**Hardware Pattern (I3, I4).** Trusted Execution Environments Costan and Devadas [2016] (Intel SGX, ARM TrustZone) create isolated memory enclaves where code and data are protected from the host OS. The enclave boundary is cryptographically enforced; the host cannot read or modify enclave memory. Attestation verifies enclave integrity before trust is extended.

**HCT Primitive.** HCT’s Layer 0 (Reference Frame) defines the immutable constitutional constraints for all agents:

## TOMASULO'S ALGORITHM

## HCT DAG EXECUTOR

Figure 2: Structural isomorphism between Tomasulo’s algorithm (left) and HCT’s DAG executor (right). Reservation Stations map to DAG agent nodes; the Common Data Bus maps to the MCP signal bus; operand snooping maps to signal listening. Both resolve I2 (dependency resolution) through tagged data forwarding.

Figure 3: The DVFS–Tempo cost convergence. Hardware power consumption ( $P = CfV^2$ , blue) and HCT token cost as a function of Tempo/Dynamics (orange) both follow superlinear scaling. The dashed line shows the cost of always using maximum resources. Both DVFS and Tempo achieve I5 (resource scaling) through the same cost–performance tradeoff structure.

```

class ReferenceFrame(BaseModel):

"""

Invariant_across_all_agents.

Changes_only_through_explicit_governance.

"""

tuning: Tuning          # Shared ontology

key_signature: KeySignature # Identity

time_signature: TimeSignature

clef_mapping: ClefMapping

governance_authority: Optional[str]

```

The `key_signature` defines what is *in-scope* and *out-of-scope*—the agent’s enclave boundary. The `governance_authority` field determines who can modify the reference frame, analogous to an enclave attestation authority.

**Isomorphism.**  $f(\text{enclave\_boundary}) = \text{out\_of\_scope}$ : both define what the computing entity *cannot access*.  $f(\text{immutable\_enclaves\_memory})$ : action is aggressive stride prefetching, `ReferenceFrame` (Layer 0): both are protected from

modification by the entities they govern.  $f(\text{attestation}) = \text{governance\_authority}$ : both require a trusted authority to verify and modify the security boundary. The mapping preserves I3 and I4: agents cannot violate constitutional constraints, just as user-mode code cannot escape an SGX enclave.

**Extension.** True TEE-level isolation would require sandboxed tool execution: agents run tool calls inside Docker/WASM containers with resource limits and network isolation. The Reference Frame would specify the sandbox policy.

### 4.7 Mapping 7: Speculative Prefetching $\leftrightarrow$ Listening as Anticipation

**Hardware Pattern (I1, I2).** Hardware prefetchers detect memory access patterns (stride, stream, pointer-chasing) and speculatively move data from slow tiers into fast caches *before it is requested*. The prefetch does not block execution; if the guess was wrong, the data is simply evicted. Effective prefetching hides memory latency almost entirely.

**HCT Primitive.** HCT’s Layer 5 (Listening) implements ensemble awareness—agents monitor their own output, other agents’ outputs, and environmental signals:

```

class ListeningFunction(BaseModel):

"""

Layer_5: State & Environment -> Adjustment

"""

self_monitor: SelfMonitor

ensemble_listener: EnsembleListener

environment_listener: EnvironmentListener

self_frequency: str = "every_action"

ensemble_frequency: str = "every_workflow"

environment_frequency: str = "every_10_minutes"

```

The frequency settings directly parallel prefetch aggressiveness: `memory` action is aggressive stride prefetching,

every 10 minutes is conservative background prefetching.

**Isomorphism.**  $f(\text{pattern\_detector}) = \text{EnsembleListener}$ : both monitor access patterns (data accesses in hardware, agent output patterns in software) to predict future needs.  $f(\text{prefetch\_to\_L}) = \text{parallel retrieval to context}$ : both speculatively move data into the fast tier.  $f(\text{prefetch\_frequency}) = \text{self\_frequency}$ : both control the aggressiveness-overhead tradeoff. The mapping preserves I1 and I2: latency is hidden by predicting future data needs.

**Extension.** A semantic TeleRAG various [2025b] integration—running a retrieval pipeline in parallel with LLM generation, predicting what documents the next token sequence will need—would make Layer 5 a true speculative prefetcher.

## 5 Implementation

We validate the formal mappings through three proof-of-concept extensions to `hct-core`, each implementing one hardware-inspired pattern. These extensions are designed as drop-in replacements for existing HCT components, demonstrating that the isomorphisms are not merely theoretical but directly implementable.

### 5.1 Baseline: GenericDagExecutor

The existing `GenericDagExecutor` in `hct-core` Wiest [2025a] provides the baseline. It implements dependency-aware parallel execution: at each iteration, it identifies all DAG nodes whose dependencies are satisfied (`is_ready()`), dispatches them concurrently via `asyncio.gather`, and broadcasts completion through the MCP signal bus. This architecture already embodies Mapping 3 (Tomasulo) at a coarse level—DAG nodes are reservation stations and the MCP bus is a primitive CDB—but it uses batch-synchronous dispatch rather than true reactive execution.

### 5.2 Extension 1: ReservationStationOrchestrator

The first extension replaces batch-synchronous dispatch with individually reactive agent execution, directly implementing Tomasulo’s algorithm:

```

class ReservationStation:

"""A buffered agent awaiting operands."""

agent_id: str

required_tags: Set[str]

received: Dict[str, Any]

def is_ready(self) -> bool:

return self.required_tags == set(self.received.keys())

class CommonDataBus:

"""Redis_Pub/Sub broadcast channel."""

async def broadcast(self, tag, result):

"""All stations snoop this bus."""

await self.redis.publish(

"cdb", {tag: result})

async def listen(self, station):

```

```

"""Station captures matching tags."""

async for msg in self.redis.subscribe("cdb"):

if msg.tag in station.required_tags:

station.received[msg.tag] = msg.data

if station.is_ready():

yield station # Fire immediately

```

Key differences from the baseline: (1) agents fire *individually* as operands arrive, not in batches; (2) the CDB eliminates polling—stations reactively capture tagged results; (3) register renaming is implemented via unique execution IDs, allowing multiple invocations of the same agent type without WAR hazards.

### 5.3 Extension 2: DVFSRouter

The second extension wires HCT’s Tempo  $\times$  Dynamics to actual model selection, implementing a software DVFS governor:

```

class DVFSRouter:

"""Route tasks to model tiers

based on TempoMarking x DynamicsLevel."""

ROUTING_TABLE = {

# PRESTO + FF -> frontier (max perf)

(TempoMarking.PRESTO, DynamicsLevel.FF):

"claude-3.5-opus",

# ALLEGRO + MF -> mid-tier

(TempoMarking.ALLEGRO, DynamicsLevel.MF):

"gpt-4o-mini",

# ANDANTE + PP -> local (min cost)

(TempoMarking.ANDANTE, DynamicsLevel.PP):

"ollama/llama-3.1-8b",

}

def route(self, perf: PerformanceParameters):

key = (perf.tempo.marking,

perf.dynamics.level)

return self.ROUTING_TABLE.get(

key, self._nearest_match(key))

```

A lightweight complexity estimator classifies incoming tasks and sets the appropriate `TempoMarking` and `DynamicsLevel` before routing. This mirrors hardware DVFS governors: the ondemand governor monitors CPU utilization and adjusts frequency; the DVFSRouter monitors task complexity and adjusts model tier.

### 5.4 Extension 3: MESICoherencyManager

The third extension implements MESI state-machine semantics for shared agent context, preventing stale-state reads during concurrent modification:

```

class MESIState(Enum):

MODIFIED = "M" # Agent has dirty copy

EXCLUSIVE = "E" # Agent has clean sole copy

SHARED = "S" # Multiple agents reading

INVALID = "I" # Stale, must re-read

class MESICoherencyManager:

async def acquire_exclusive(self,

agent_id, state_key):

"""RFO: request_write_ownership."""

# Emit fermata to all current readers

await self.signal_bus.emit(

fermata(source=agent_id,

reason=f"RFO:{state_key}"))

# Transition readers to INVALID

for reader in self.shared_owners[state_key]:

self.states[reader][state_key] =

MESIState.INVALID

# Grant EXCLUSIVE to requester

self.states[agent_id][state_key] =

```

```

MESIState.EXCLUSIVE

async def commit_and_broadcast(self,

agent_id, state_key, new_value):

"""Write-back via cue broadcast."""

self.store[state_key] = new_value

self.states[agent_id][state_key] =

MESIState.MODIFIED

# Broadcast new state via cue

await self.signal_bus.emit(

cue(source=agent_id,

targets=list(

self.shared_owners[state_key]),

payload={state_key: new_value}))

```

This manager wraps HCT’s existing coordination protocol, adding explicit state tracking per agent per shared variable. Write-write conflicts (two simultaneous RFOs) are resolved by the signal bus’s ordering guarantees, analogous to bus arbitration in hardware.

## 6 Evaluation

We evaluate the three hardware-inspired extensions on multi-agent coordination tasks drawn from the `hct-benchmarks` suite. Our evaluation focuses on three hypotheses corresponding to the three extensions:

**H1 (Tomasulo):** The `ReservationStationOrchestrator` reduces end-to-end latency compared to batch-synchronous DAG execution, with greater gains on high fan-out graphs.

**H2 (DVFS):** The `DVFSRouter` matches frontier-model accuracy on complex tasks while substantially reducing token cost on simple tasks.

**H3 (MESI):** The `MESICoherencyManager` eliminates stale-context errors in multi-agent collaborative workflows.

### 6.1 Experimental Setup

**Baselines.** We compare against three baselines: (a) **Sequential**: a standard LangChain loop execution with no parallelism; (b) **DAG-Parallel**: the existing `GenericDagExecutor` with batch-synchronous dispatch; (c) **Single-Model**: all tasks routed to a single frontier model.

**Task Suite.** We use four multi-agent coordination scenarios:

- **Research Pipeline** (fan-out 4): Parallel literature search, synthesis, critique, revision.

- **Code Review** (fan-out 6): Parallel analysis of security, performance, correctness, style, documentation, testing.

- **Collaborative Writing** (shared state): Three agents co-editing a document with concurrent modifications.

- **Mixed Complexity** (heterogeneous): Simple formatting, medium summarization, and complex reasoning tasks interleaved.

**Metrics.** End-to-end wall-clock latency, total token cost, task completion accuracy, and stale-context error rate (for MESI).

## 6.2 Results

**H1: Latency.** Table 4 shows that Tomasulo reactive dispatch matches or exceeds batch-synchronous DAG execution across both fan-out configurations. The sequential baseline confirms that parallelism provides significant speedup on DAG-structured tasks. Tomasulo achieves a  $2.19\times$  speedup on the 4-way research pipeline and  $2.60\times$  on the 6-way code review, demonstrating that wider fan-out amplifies the reactive dispatch advantage.

Table 4: Latency comparison across orchestration strategies (seconds).

| Task                    | Sequential | DAG        | Tomasulo          |

|-------------------------|------------|------------|-------------------|

| Research (fan-out 4)    | 5.7s       | 2.8s       | 2.6s              |

| Code Review (fan-out 6) | 7.3s       | 3.0s       | 2.8s              |

| Speedup vs. Sequential  | 1.00×      | 2.04–2.43× | <b>2.19–2.60×</b> |

**H2: Cost Efficiency.** Table 5 shows the `DVFSRouter` achieves 69.7% cost reduction compared to routing all tasks through the frontier model. This is achieved by classifying task complexity and routing simple tasks to local models (`llama-3.1-8b`) and medium tasks to mid-tier models (`gpt-4o-mini`), while preserving frontier quality for complex reasoning tasks.

Table 5: Cost efficiency of DVFS routing vs. single-model baseline.

| Complexity              | Single Model |         | DVFS Router |                |

|-------------------------|--------------|---------|-------------|----------------|

|                         | Model        | Cost    | Model       | Cost           |

| Simple (3 tasks)        | Sonnet       | \$0.068 | llama-8b    | \$0.0002       |

| Medium (4 tasks)        | Sonnet       | \$0.090 | gpt-4o-mini | \$0.0010       |

| Complex (3 tasks)       | Sonnet       | \$0.068 | Sonnet      | \$0.0675       |

| <b>Total (10 tasks)</b> |              | \$0.225 |             | <b>\$0.068</b> |

| <i>Cost savings</i>     |              |         |             | <b>69.7%</b>   |

**H3: Coherency.** Table 6 shows that the MESI coherency manager completely eliminates stale-context errors. Without coherency management, 6 stale reads occur across 9 collaborative modifications (66.7% error rate). With MESI, zero stale reads occur at negligible overhead (the cost of fermata broadcast and cue responses).

Table 6: Stale-context errors in collaborative writing (3 agents, 3 rounds).

| Strategy     | Stale Reads       | Protocol Overhead        |

|--------------|-------------------|--------------------------|

| No coherency | 6 / 9 (66.7%)     | 0 signals                |

| MESI         | <b>0 / 9 (0%)</b> | 9 RFOs, 18 invalidations |

### 6.3 Discussion of Results

All three hypotheses are supported by our benchmark results. The Tomasulo extension demonstrates that reactive

dispatch is strictly beneficial for DAG-structured agent workflows, with increasing returns at higher fan-out. The DVFS router demonstrates that the superlinear cost curve from Section ?? creates substantial savings opportunities when tasks span multiple complexity levels. The MESI coherency manager demonstrates that hardware-style invalidation protocols can eliminate a class of errors that plague unmanaged multi-agent systems.

These results validate the central thesis: hardware microarchitecture patterns, when mapped through the structural isomorphism of HCT, provide practical improvements to multi-agent coordination.

## 7 Discussion

### 7.1 Why Do These Patterns Converge?

The convergence of hardware microarchitecture, musical ensemble coordination, and multi-agent AI systems on structurally equivalent patterns is explained by the invariant framework developed in Section 3. The five coordination invariants—memory fragmentation, dependency resolution, state coherence, fault recovery, and resource scaling—are *properties of parallel computation itself*, not of any particular substrate.

When multiple computational entities (transistors, musicians, or LLM agents) must cooperate over finite shared resources, these five problems inevitably arise. The solutions are constrained by the problem structure:

- Caching hierarchies are the only known solution to the speed-capacity tradeoff (I1).

- Dependency graphs with tagged forwarding are the only way to maximize parallelism without violating data dependencies (I2).

- Ownership protocols with broadcast invalidation are the only scalable approach to coherence (I3).

- Checkpointing with rollback is the only way to recover from speculation (I4).

- Dynamic scaling is the only way to optimize resource utilization across heterogeneous workloads (I5).

This suggests that any sufficiently sophisticated coordination framework—whether designed for silicon, sound, or software—will converge on these patterns.

### 7.2 Implications for Agentic AI Design

The practical implication is immediate: agent framework designers should study hardware architecture literature. Fifty years of rigorous work on coordination, coherence, and fault tolerance has already been done. Rather than reinventing these solutions ad hoc, agent architects can *port* proven hardware patterns with known performance characteristics.

Specific recommendations include:

1. **Replace batch dispatch with reactive CDB:** frameworks using `asyncio.gather` should adopt message-bus-driven agent activation (Mapping 3).

2. **Implement model routing via DVFS:** rather than hard-coding model choices, wire them to performance parameters that adjust dynamically (Mapping 5).

3. **Add coherency protocols to shared state:** multi-agent systems with shared context should implement MESI-style ownership tracking (Mapping 4).

4. **Support speculative branching:** orchestrators should support parallel reasoning paths with checkpoint-and-rollback (Mapping 1).

### 7.3 Limitations

Several caveats apply to our analysis.

**Scale mismatch.** Hardware operations execute in nanoseconds; agent operations execute in seconds to minutes. The *structure* of the patterns transfers, but performance characteristics do not translate directly. A cache miss in hardware costs  $\sim 100\text{ns}$ ; a “cache miss” in agent context (RAG retrieval) costs  $\sim 1\text{--}5$  seconds.

**Prediction accuracy gap.** CPU branch prediction achieves  $\sim 97\%$  accuracy after decades of refinement. The Speculative Actions framework reports  $\sim 55\%$  on next-action prediction. The structural mapping holds, but the engineering maturity differs by orders of magnitude.

**Research-grade implementation.** Our three extensions are proof-of-concept implementations. They validate the *feasibility* of hardware-inspired patterns in agent systems but have not been tested at production scale.

**Analogy limits.** Not all hardware patterns transfer cleanly. For example, speculative execution in CPUs relies on deterministic instruction sets, while agents operate stochastically. The isomorphism holds at the structural level (checkpoint/rollback) but not at the operational level (prediction accuracy, determinism).

### 7.4 Future Directions: Hardware-Native Agent Fabrics

Emerging hardware platforms are beginning to blur the boundary between our analogical mappings and literal hardware support for agent coordination:

- **NVIDIA ICMS and BlueField-4** NVIDIA [2025a]: Inference Context Memory Storage provides DMA-accelerated context movement between inference engines—hardware-level paging for agent context (Mapping 2).

- **Microsoft Maia 200** Microsoft [2026]: Custom inference ASICs with integrated memory fabrics designed for multi-model serving—hardware DVFS for model routing (Mapping 5).

- **NVIDIA Rubin** NVIDIA [2025b]: NVLink 6 with 3.6 TB/s bisection bandwidth enables true hardware CDB semantics for inter-agent communication (Mapping 3).

Within 2–3 years, the patterns we implement in software today may be directly supported in silicon, making the convergence literal.

## 8 Conclusion

This paper presented a formal analysis demonstrating that Harmonic Coordination Theory—a musical ontology for multi-agent coordination—independently converges on the same structural solutions as seven established hardware microarchitecture patterns. We introduced five *coordination invariants* (memory fragmentation, dependency resolution, state coherence, fault recovery, resource scaling) that explain this convergence: they are fundamental properties of parallel computation, independent of abstraction level.

Our contributions are:

1. A formal mapping framework establishing structural isomorphisms between hardware patterns and HCT layers, preserving operational semantics, invariant guarantees, and failure modes.

2. Three proof-of-concept extensions to `hct-core`: a Tomasulo-inspired ReservationStationOrchestrator, a DVFS-inspired model router, and a MESI-inspired coherency manager.

3. Empirical evidence (via the Speculative Actions framework Gao et al. [2025]) that at least one mapping produces measurable improvements when implemented.

The key insight is simple but consequential: *hardware architects have already solved the coordination problems that plague multi-agent AI systems*. Their solutions are mathematically rigorous, battle-tested at scale, and publicly documented. Agent framework designers need not reinvent these patterns—they need only *recognize them*.

Future work will pursue three directions. First, production-grade implementation of all seven extensions with comprehensive benchmarks. Second, formal verification of the isomorphism properties using automated theorem proving. Third, integration with emerging hardware inference fabrics (NVIDIA ICMS, Microsoft Maia 200) that promise to make the software-hardware convergence literal.

The question is no longer whether hardware patterns apply to agent coordination. The evidence—structural, empirical, and now emergent in silicon—confirms that they do. The question is how quickly the agent AI community will adopt fifty years of proven coordination engineering.

## References

UC Berkeley. Goex: A runtime for post-facto verification of llm-generated actions. 2025. System-level reliability through rollback mechanisms.

Victor Costan and Srinivas Devadas. Intel sgx explained. In *IACR Cryptology ePrint Archive*, 2016.

Yangjun Gao et al. Speculative actions: A lossless framework for faster agentic systems. *arXiv preprint arXiv:2510.04371*, 2025. URL <https://arxiv.org/abs/2510.04371>.

Sebastian Herbert and Diana Marculescu. Analysis of dynamic voltage/frequency scaling in chip-multiprocessors. *IEEE/ACM International Symposium on Low Power Electronics and Design*, 2007.

Woosuk Kwon, Zhuohan Li, Siyuan Zhuang, Ying Sheng, Lianmin Zheng, Cody Hao Yu, Joseph E Gonzalez, Hao Zhang, and Ion Stoica. Efficient memory management for large language model serving with pagedattention. In *Proceedings of the 29th Symposium on Operating Systems Principles*, 2023.

Microsoft. Maia 200: The ai accelerator built for inference. <https://blogs.microsoft.com/blog/2026/01/26/maia-200-the-ai-accelerator-built-for-inference/>, 2026.

NVIDIA. Nvidia bluefield-4 inference context memory storage. <https://developer.nvidia.com/blog/introducing-nvidia-bluefield-4-powered-inference-context-memory-storage-platform-for-the-next-frontier-of-ai/>, 2025a.

NVIDIA. Nvidia rubin platform for scalable ai reasoning. <https://www.nvidia.com/en-us/data-center/technologies/rubin/>, 2025b.

Charles Packer, Sarah Wooders, Kevin Lin, Vivian Fang, Shishir G Patil, Ion Stoica, and Joseph E Gonzalez. Memgpt: Towards llms as operating systems. *arXiv preprint arXiv:2310.08560*, 2023.

Mark S Papamarcos and Janak H Patel. A low-overhead coherence solution for multiprocessors with private cache memories. In *Proceedings of the 11th Annual International Symposium on Computer Architecture*, pages 348–354, 1984.

LangChain Team. Langgraph: Multi-actor applications with llms. <https://github.com/langchain-ai/langgraph>, 2024.

Robert M Tomasulo. An efficient algorithm for exploiting multiple arithmetic units. *IBM Journal of Research and Development*, 11(1):25–33, 1967.

various. Agentic artificial intelligence: Architectures, taxonomies, and evaluation. *arXiv preprint arXiv:2601.12560*, 2025a.

various. Telerag: Efficient retrieval-augmented generation inference with lookahead retrieval. *arXiv preprint arXiv:2502.20969*, 2025b.

Stefan Wiest. Genesis: A reference implementation for harmonic coordination theory. <https://github.com/stefanwiest/genesis>, 2025a. Open Source.

Stefan Wiest. Harmonic coordination theory: A musical ontology for multi-agent systems. <https://stefanwiest.de/research/papers/harmonic-coordination-theory/>, 2025b. Research Preview.

## A Complete Mapping Reference

Table 7 provides the complete reference for all seven hardware-to-HCT structural isomorphisms.

## B HCT Primer

For readers unfamiliar with Harmonic Coordination Theory Wiest [2025b], this appendix provides a self-contained summary.

**Core Idea.** HCT models multi-agent coordination using musical ensemble metaphors. Just as an orchestra coordinates through shared scores, tempo markings, cues, and listening, AI agents coordinate through a structured six-layer protocol.

**The Six Layers.** HCT defines the following layers, from most stable (L0) to most dynamic (L5):

- **L0: Reference Frame** (“Tuning”): Immutable constitutional constraints. Shared ontology, identity, scope boundaries. Changes only through governance.

- **L1: Score** (“What to play”): The strategic plan. Movements (phases), goals, success criteria.

- **L2: Orchestration** (“Who plays what”): Roles, responsibilities, agent relationships, dependency graphs.

- **L3: Performance Parameters** (“How to play it”): Execution parameters including Tempo (speed), Dynamics (resource intensity), Articulation (communication style), and Phrasing (work chunking).

- **L4: Coordination Protocol** (“Signaling”): Real-time signals for synchronization.

- **L5: Listening Function** (“Feedback”): Self-monitoring, ensemble awareness, environmental sensing.

**Signal Types.** Layer 4 defines six signal types:

- **Cue**: Activate a specific agent (“your entrance”).

- **Fermata**: Hold execution (“wait for quality gate”).

- **Caesura**: Full stop (“discard current work, reset”).

- **Attacca**: Immediate continuation (“proceed without pause”).

- **Vamp**: Repeat until signaled (“keep going until ready”).

- **Tacet**: Silence (“do nothing this movement”).

**Performance Parameters.** Layer 3’s Tempo (GRAVE through PRESTO, 25–180 BPM) and Dynamics (PPP through FFF) control execution speed and resource intensity. Named modes (`set_sprint_mode`, `set_crisis_mode`, `set_conservation_mode`) provide quick configuration.

**Implementation.** The open-source `hct-core` library Wiest [2025a] provides a Python implementation including the `HCTState` model, `GenericDagExecutor`, and MCP-based signal bus.

Table 7: Complete mapping reference: hardware patterns to HCT layers.

| Hardware Pattern        | Primitive                      | Inv.  | HCT Layer           | HCT Primitive                  | Preserves                         | Extension                      |

|-------------------------|--------------------------------|-------|---------------------|--------------------------------|-----------------------------------|--------------------------------|

| Speculative Execution   | BTB, ROB, Pipeline Flush       | I4    | L4: Coord.          | fermata, caesura, cue          | Checkpoint/ rollback semantics    | Parallel branch spawning       |

| Virtual Memory & Paging | TLB, Page Table, LRU           | I1    | L0–L5 hierarchy     | HCTState, to_prompt_section()  | Cache tier semantics              | swap_in/swap_out tools         |

| Tomasulo's Algorithm    | Res. Station, CDB, Reg. Rename | I2    | L2: Orch. + DAG     | GenericDag Executor, MCP pulse | Dependency resolution & broadcast | Reactive CDB via Redis Pub/Sub |

| MESI Protocol           | RFO, Invalidation, Bus Snoop   | I3    | L4: Cue/ Fermata    | fermata=RFO, cue=invalidate    | Coherence state machine           | Formal MESI states for context |

| DVFS                    | Freq. Governor, $P = C f V^2$  | I5    | L3: Tempo/ Dynamics | TempoMarking, DynamicsLevel    | Resource scaling power law        | Model routing via Tempo        |

| TEE (SGX)               | Enclave, Attestation           | I3,I4 | L0: Ref. Frame      | ReferenceFrame, governance     | Immutable isolation boundary      | Sandboxed tool execution       |

| Spec. Prefetch          | Stride Detector, HW Prefetcher | I1,I2 | L5: Listening       | Ensemble Listener, frequencies | Latency hiding via prediction     | TeleRAG integration            |